芯片资讯

- 发布日期:2024-01-03 09:52 点击次数:185

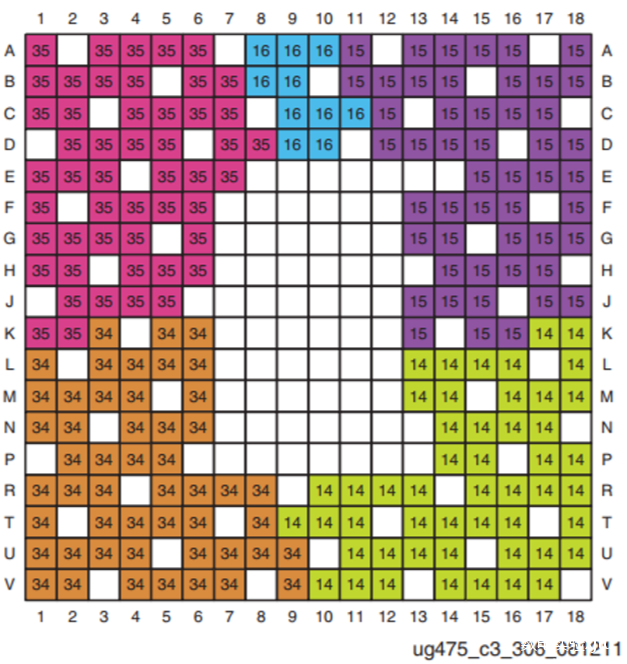

FPGA的引脚排布在芯片背面,以EGO1板载芯片XC7A35T-1CSG324C 为例,下图中每个小格代表一个引脚,共有18行18列,共324个引脚。

XC7A35T I/O Bank

FPGA引脚命名通过英文+数字的方式,英文表示所在行,数字表示所在列。

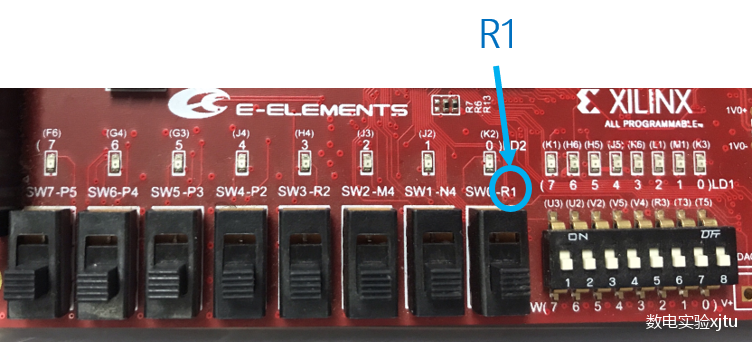

在EGO1上可以看到,在每一个通用IO的丝印标识名称旁边都有一个英文加数字的标识,就是该外设与FPGA相连接的引脚名称。每一个外设与FPGA的具体连接,在EGO1开发板的电路原理图中都可以找到。

例如,开关SW0连接的是FPGA的R1引脚。当使用SW0作为输入时,就是要读入R1引脚的状态。因此, EEPROM带电可擦可编程存储器芯片大全在vivado设计中,CMOS图像传感器集成电路芯片进行管脚约束时, 芯片交易网IC交易网要将模块的输入端口约束到R1引脚上。

XC7A35T-1CSG324C所有324个引脚包括了:

① 210个用户可用引脚。这些引脚被划分为50个一组的Bank, ATMEGA系列ATMEL芯片COM在I/O Bank 图中, 电子元器件PDF资料大全同一颜色的引脚为一个Bank。可以看出该芯片有5个Bank,分别是Bank34,亿配芯城官网Bank35,Bank15,Bank14,以及部分bank16。这些引脚都可以作为普通IO使用,其中有一些是多功能引脚,当有特殊要求时,只能使用相对应功能的IO,例如差分输入引脚,高时钟输入引脚等等。

② I/O Bank 图中,空白没有标注的引脚为专用引脚(芯片配置,全局时钟)和电源引脚,有固定的功能和作用,用户不能占用。中间空白的部分主要是内核电压、辅助电压,Bram电压的供电引脚。

③ 每个I/O Bank中,有一些白色小方块,这些空白处大都是I/O的电源和地 ,不同的I/O Bank可以使用不同的电平标准单独供电。外部信号输入FPGA的电平、IO Bank供电电压和约束文件里声明必须一致。

- 全球FPGA芯片市场布局2025-10-08

- Cyclone系列FPGA:高性能可编程逻辑解决方案的技术解析与应用场景2025-08-25

- 电子电路元器件套装与原理图解析:芯片分销商模式如何赋能电子设计2025-05-06

- tps5430引脚图及引脚说明2024-11-29

- 8255接口芯片的引脚图及引脚功能的详细资料概述2024-11-25

- 如何将光强度转换为一个电学量2024-11-21