芯片资讯

- 发布日期:2024-01-03 09:06 点击次数:205

Vivado是Xilinx公司2012年推出的新一代集成开发环境,它强调系统级的设计思想及以IP为核心的设计理念,突出IP核在数字系统设计中的作用。

01

什么是IP核

随着电子设计自动化工具功能的不断增强,以及半导体制造工艺的飞速发展,所设计的数字系统功能越来越复杂,所要求的设计周期越来越短,设计可靠性越来越高。对设计人员来说,不可能从头开始进行复杂数字系统的设计。目前普遍采用的方法是,在设计中尽可能使用已有的功能模块。人们把这些现成的模块通常称为知识产权(Intellectual Property,IP)核,也就是IP核。IP核可以理解为一个个具有特定功能的电路模块,通过这些模块间端口的互联完成功能复杂的数字系统设计。

02

IP核来源

①IP核可以来自FPGA生产厂商,例如,Vivado设计工具中的IP目录中就提供了丰富的IP核,可以直接使用。

②IP核还可以是第三方IP厂商提供。

③我们也可以将自己设计的,经过验证的电路模块封装成IP核,可以在后期设计中重复使用。

我们自己的设计包括:

RTL代码描述的电路。

HLS高层次综合工具的设计。

Syetem Generator工具生成的工程。

03

IP核如何使用

那么我们如何在Vivado中使用IP核呢?

有两种方式:

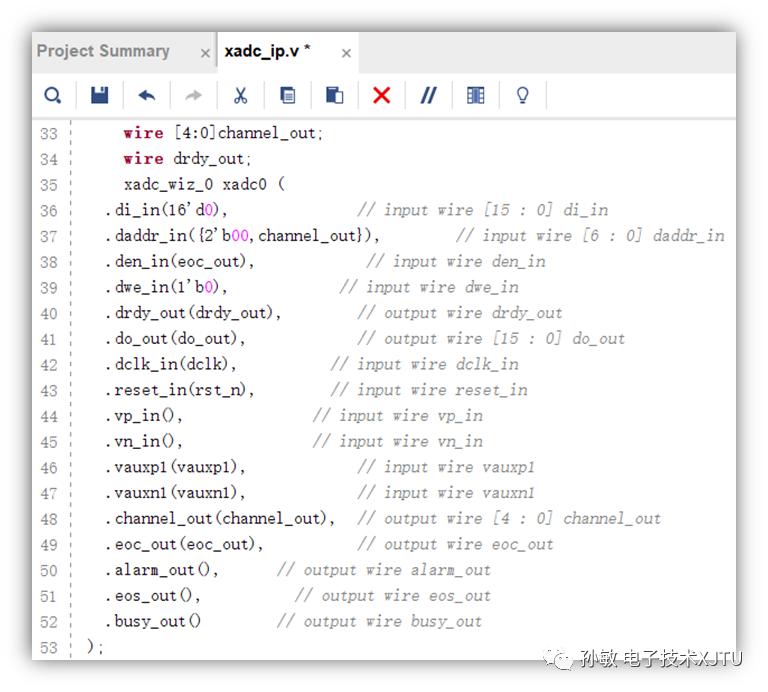

①一种是在RTL工程中,在我们的Verilog设计程序中调用IP核,我们叫做实例化IP。

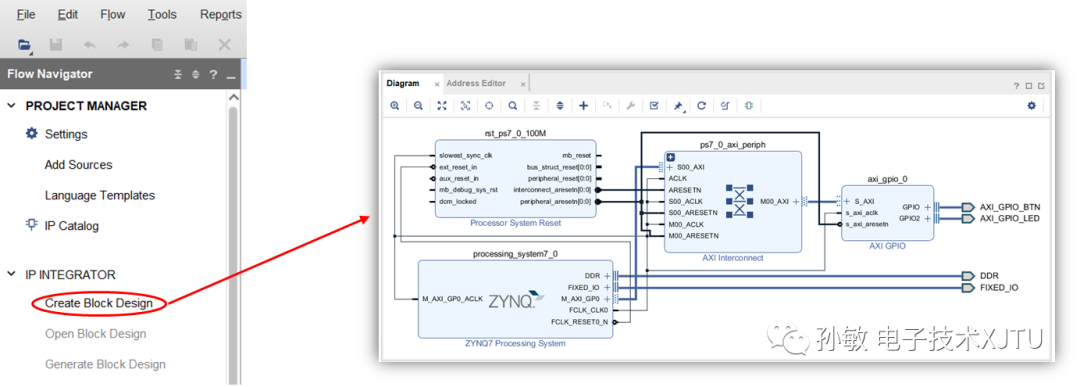

△ 实例化IP

②一种是在IP Integrator中,也就是使用IP集成器创建一个Block Design, 芯片交易网IC交易网可以将IP核, ATMEGA系列ATMEL芯片COM以图形化的方式添加到界面中, 电子元器件PDF资料大全再通过端口的互联, EEPROM带电可擦可编程存储器芯片大全像搭积木一样完成一些复杂的设计。

04

Vivado设计输入

在Vivado中,CMOS图像传感器集成电路芯片我们有多种方式来进行我们的设计输入。

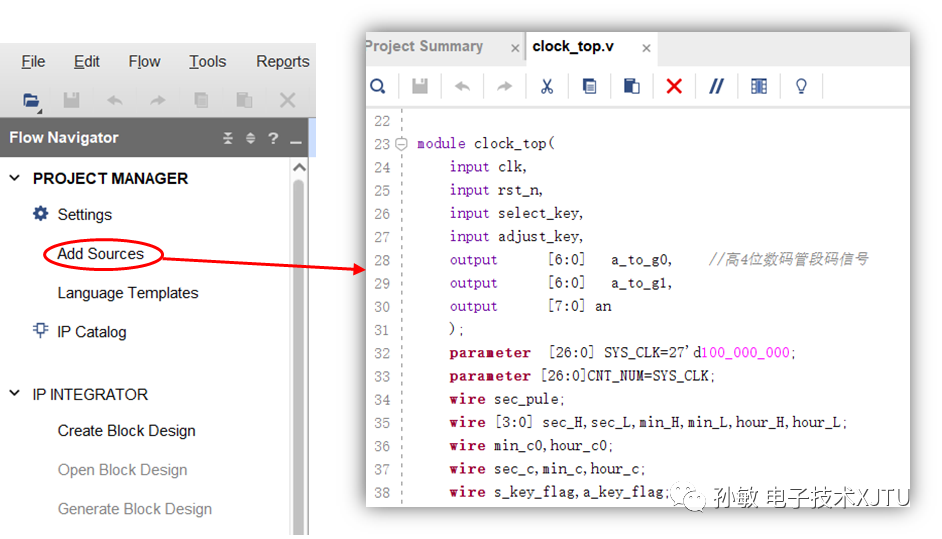

RTL工程

通常使用的方法是创建RTL工程,使用硬件描述语言编写代码。所谓的RTL是Register Transfer Level 的缩写,也就是寄存器传输级。

△ 创建RTL工程

我们在描述一个数字系统时,可以采用不同的抽象层级,抽象程度从高到低有系统级、算法级,RTL级,亿配芯城官网逻辑门级,以及开关级。

RTL级设计是描述数据信号是如何在寄存器中传输和处理的,一般都是通过硬件描述语言实现的。如,最常使用的Verilog 和VHDL,以及近年来,发展起来的System Verilog。

System Verilog实际上是Verilog的超集,可以被看做是Verilog的升级加强版,尤其加强了对设计验证的支持,在现代数字系统设计与验证广泛使用。

IP集成器

另一种方式就是通过IP集成器,可以将IP核添加到图形化界面中,再通过连线完成设计,这里的IP来自于IP目录中的IP核。

△ 通过IP集成器创建工程

高层次综合(HLS)工具

Xilinx还推出了Vivado High-Level Synthesis (HLS)高层次综合工具,用户可以使用C或C++ 来对FPGA编程,实现算法开发,然后通过高级综合工具直接将C语言转换为硬件描述语言,可以大大加速我们的设计,提高开发效率。HLS会将转换后的RTL代码封装成IP,我们可以将其添加到IP 目录中,在Vivado设计输入时使用。

System Generator

Vivado还提供了System Generator 工具,该工具是基于MATLAB下的Simulink工具运行的。他将Xilinx开发的一些模块嵌入到了Simulink中,主要用于数字信号处理开发。在Simulink中设计完成后,可以生成HDL文件,包括测试文件,能够加快DSP系统的开发进度。

05

基于IP的设计

Vivado HLS的输出结果也可以导入到System Generator中,以模块化的方式使用。

Vivado中的IP packaging功能可以将我们的RTL代码,High Level Symthesis设计,System Generator模块以及IP集成器生成的设计封装成新的IP,放到IP目录中使用。

所以说,Vivado是基于IP的设计。

- 基于C51单片机的通信测试仪器设计2024-11-22

- 基于FPGA器件和DSP系统实现自适应回波抵消器的设计2024-11-06

- 基于CAN总线和CAN8423控制器实现切水器的开发和应用2024-11-02

- 晶振为什么不能放置在PCB边缘?2024-10-17

- 基于FPGA芯片XC4005E-4IPQ100实现频信号发送系统的方案设计2024-09-24

- 基于DSP器件TMS320F2812实现同步采样模块的方案设计2024-09-18